Understanding Chip Scale Package (CSP): Key Features, Advantages, and Challenges

As electronics continue to shrink, the need for packaging that can keep up with the demand for smaller, more powerful devices has never been more critical. Chip Scale Packaging (CSP) is at the heart of this evolution, offering a compact solution that blends high performance with remarkable space efficiency. From wearables to medical implants, CSP enables cutting-edge technologies to fit into the tiniest of spaces without compromising on functionality. This isn't just about shrinking sizes—it's about unlocking new possibilities for innovation in the most unexpected places. Let's explore how CSP is making this revolution possible.

Introduction to Chip Scale Package (CSP)

Definition: Overview of CSP as the Smallest Form of Semiconductor Packaging

Chip Scale Packaging (CSP) refers to a type of semiconductor package that is designed to be nearly the same size as the chip it contains. Unlike traditional packaging methods that add extra material around the chip, CSP minimizes the additional size, typically not exceeding 1.2 times the size of the chip itself. This makes CSP one of the smallest and most compact packaging solutions available for electronic components.

CSP is achieved using wafer-level packaging (WLP) or flip-chip bonding, which directly places the chip onto the package, reducing space and material waste. This packaging is especially useful in situations where space is extremely limited, such as in wearables, smartphones, or medical implants.

Key Points:

CSP: Small, efficient packaging for semiconductor chips.

Wafer-Level Packaging or Flip-Chip Bonding: Techniques that minimize size and waste.

Compact and space-saving: Used in devices where size matters.

Importance: Role of CSP in Miniaturization of Electronic Devices

CSP plays a pivotal role in the miniaturization of electronic devices. As the demand for smaller, more powerful gadgets increases, manufacturers must find ways to shrink the size of the components without sacrificing performance. CSP enables this by reducing the space required for packaging, which in turn allows more room for other parts of the device, like batteries or sensors.

For example, in smartwatches, where the goal is to fit advanced processing power into a small form factor, CSP is the ideal solution. Without CSP, a watch would have to be much larger to accommodate traditional semiconductor packaging. Similarly, medical devices like pacemakers or hearing aids, which need to be compact yet reliable, benefit greatly from CSP’s small footprint and high performance.

Key Points:

CSP helps shrink component sizes for smaller devices.

Smartwatches and medical devices benefit from the space-saving nature of CSP.

Smaller packaging allows for more functionality in compact designs.

Why CSP Matters: How It Enables the Development of Compact, High-Performance Devices

CSP is more than just a solution for reducing physical size; it is key to achieving high performance in tiny devices. By using advanced bonding techniques like flip-chip, CSP ensures that connections between the chip and the package are short and efficient. This reduces signal loss and heat generation, making CSP ideal for devices that need to run efficiently despite their small size.

In smartphones, where both performance and space are crucial, CSP enables high-speed processors, sensors, and memory to function smoothly in a compact form. For instance, CSP is often used in camera sensors inside smartphones, where performance (like fast image processing) is critical, but the space available for components is minimal.

Moreover, CSP reduces manufacturing costs in high-volume production due to its efficient use of materials and streamlined process. This makes it a cost-effective option for mass-producing small, high-performance devices, benefiting both manufacturers and consumers alike.

Key Points:

CSP improves performance by reducing signal loss and heat.

High-speed processors and sensors in smartphones use CSP for optimal function.

Cost-effective for high-volume production, making it ideal for consumer electronics.

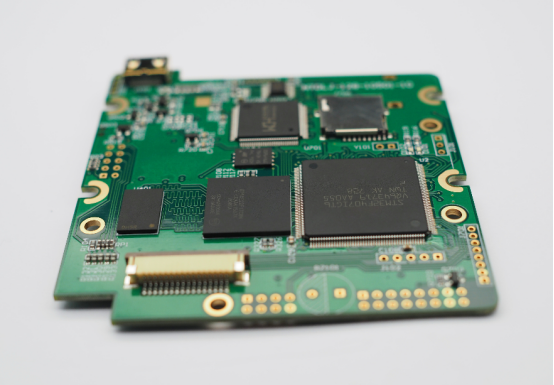

Key Features of Chip Scale Packaging (CSP)

1.Ultra-Compact Form Factor

Size Comparison: CSP vs. Traditional Packages (e.g., SOP, BGA)

CSP is one of the smallest semiconductor packaging methods available today. Unlike traditional packages like SOP (Small Outline Package) or BGA (Ball Grid Array), which add extra material around the chip, CSP keeps the size of the package as close as possible to the chip itself. Typically, CSP is no more than 1.2 times the size of the chip. For example, a 2.5mm chip might be packed into a 3mm CSP, whereas a traditional SOP for the same chip could be as large as 5mm. This compact size allows for more efficient use of space in small devices.

Advantages of Small Size: Ideal for Miniaturized Devices

The ultra-compact size of CSP is crucial for modern electronic devices, especially where space is limited. For instance, smartwatches, IoT sensors, and medical devices like pacemakers or hearing aids require small, efficient components. By using CSP, manufacturers can create high-performance devices without sacrificing space or functionality. A smartwatch, for example, needs to house a tiny chip with minimal additional bulk, making CSP the perfect solution.

Key Points:

CSP is smaller than traditional packages like SOP and BGA.

Ideal for devices where space is a premium (smartwatches, IoT devices, medical implants).

2. Wafer-Level Packaging (WLP)

What is Wafer-Level Packaging?

Wafer-Level Packaging (WLP) is a manufacturing process where the semiconductor chip is packaged directly on the wafer before it is cut into individual chips. This process eliminates the need for additional materials around the chip, leading to a smaller, thinner package. Instead of packaging each chip separately, the entire wafer is processed and tested, which improves the overall efficiency and consistency of the packaging.

Impact on Cost and Performance

By using WLP, manufacturers can lower costs and improve performance. The wafer-level process is faster and more cost-effective compared to traditional packaging methods, which require multiple stages. Since the chip is packaged directly on the wafer, the overall profile of the device is thinner. This makes CSP an excellent choice for creating slim devices like wearables. Additionally, WLP increases reliability by reducing the number of assembly steps, which can reduce the chance of defects.

Key Points:

WLP minimizes extra materials around the chip, making it thinner and cheaper.

The process reduces manufacturing steps, improving reliability and performance.

3. Advanced Bonding Methods

Flip-Chip Bonding: Explanation and Role in Performance Optimization

One of the key advantages of CSP is flip-chip bonding, a technique where the semiconductor chip is flipped upside down and connected directly to the substrate (the package) using solder bumps. This bonding method creates very short electrical connections between the chip and the package, reducing the length and resistance of the signals. Flip-chip bonding is commonly used in high-performance applications, such as smartphones and high-speed processors, where fast signal transmission is essential.

Electrical and Thermal Efficiency

The short electrical connections in flip-chip bonding help reduce signal loss and inductance, ensuring faster data transfer. This is especially important in devices that handle high-frequency data, like 5G phones or advanced processors. Additionally, because the connections are short and direct, there is less heat generated compared to traditional packaging methods. This makes CSP suitable for devices that require both high performance and low heat generation, such as gaming consoles or AR devices.

Key Points:

Flip-chip bonding connects the chip directly to the package, reducing signal loss.

Short connections improve performance and reduce heat dissipation in high-speed devices.

4. Variants of CSP

WLCSP (Wafer-Level Chip Scale Package)

WLCSP is the smallest version of CSP, where the chip is packaged directly at wafer level without additional frame or lead. It is widely used in consumer electronics like smartphones and wearables, where minimizing space is crucial. WLCSP is also ideal for sensor applications, such as in camera sensors or accelerometers, where compact size and high performance are necessary.

LFCSP (Lead Frame Chip Scale Package)

LFCSP uses a lead frame structure to support the chip and provide better thermal management. This variant is often used in power integrated circuits (ICs), such as those found in wearables and portable medical devices. The lead frame offers improved heat dissipation, making LFCSP ideal for devices that generate heat during operation, like power management ICs in smartwatches or portable health monitors.

FCCSP (Flip Chip Chip Scale Package)

FCCSP is a variant that uses flip-chip technology, but it is designed for applications that require a high number of pins, such as 5G devices or augmented reality (AR) glasses. It allows for more efficient connection of complex components with a large number of electrical contacts. FCCSP is ideal for SoCs (System on Chips) where performance and high pin count are critical, and it helps in managing the higher data throughput needed for 5G communication and AR technologies.

Comparison Table of CSP Variants:

| Variant | Features | Best Use Case |

| WLCSP | Smallest form, wafer-level packaging | Smartphones, IoT Sensors, Wearables |

| LFCSP | Lead frame, improved thermal management | Power Management ICs, Portable Health Devices |

| FCCSP | Flip-chip bonding, high-pin density | 5G Devices, AR Glasses, Complex SoCs |

Key Points:

WLCSP is the smallest and used in compact consumer electronics.

LFCSP provides better thermal management, ideal for power ICs and medical devices.

FCCSP uses flip-chip bonding for high-pin-count applications like 5G and AR devices.

Advantages of CSP Technology

1. Space Efficiency

50-70% Smaller than Traditional Packages: Comparison with BGA, SOP

One of the biggest advantages of CSP is its ability to save space. CSP packages are typically 50-70% smaller than traditional packaging methods like BGA or SOP. For example, a traditional SOP package might be twice the size of the chip it holds, whereas CSP keeps the package size nearly the same as the chip itself. This space-saving characteristic is crucial for devices like smartwatches or IoT sensors, where there is limited space for components but still a need for high performance.

Enabling Compact Device Design: How CSP Facilitates Ultra-Thin Devices like Earbuds

The small size of CSP makes it ideal for creating ultra-thin devices. In earbuds, for instance, the internal space is limited, yet they must house processors, sensors, and batteries. With CSP, manufacturers can fit all of these components into a smaller space without making the device bulky. CSP allows for better use of the available space in these tiny devices, making them not only smaller but also more functional.

Key Points:

CSP is 50-70% smaller than traditional packaging like BGA and SOP.

CSP is essential for space-constrained devices like smartwatches and earbuds.

2. High Performance and Reliability

Signal Integrity and Speed: CSP’s Role in High-Speed Data Transmission

CSP’s advanced bonding methods, like flip-chip bonding, help maintain signal integrity and improve data transmission speed. By reducing the distance between the chip and the package, CSP minimizes the time it takes for electrical signals to travel, which is crucial for high-speed applications. For instance, 5G smartphones rely on CSP to ensure fast data transfer rates. In these devices, even small delays in signal transmission can lead to slowdowns in performance.

Reduced Inductance and Resistance: Technical Explanation of Flip-Chip Bonding Reducing Signal Loss

Flip-chip bonding in CSP technology helps reduce both inductance and resistance, two factors that can slow down electronic signals. The direct connection between the chip and the substrate eliminates the need for longer wire connections, which typically increase resistance and cause signal loss. By reducing these issues, CSP allows devices to perform at their best, especially in high-frequency applications like gaming consoles, high-speed processors, and networking equipment. This improvement in performance makes CSP an ideal choice for devices that require fast, reliable data transmission.

Key Points:

CSP improves signal speed and integrity, essential for 5G devices and high-speed electronics.

Flip-chip bonding reduces signal loss by lowering inductance and resistance.

3. Cost Efficiency for High-Volume Production

Cost-Effective Manufacturing: The Role of Wafer-Level Packaging in Reducing Manufacturing Costs

One of the main reasons CSP is gaining popularity is its cost-effectiveness in mass production. The wafer-level packaging process used in CSP allows manufacturers to handle large batches of chips at once, rather than packaging them individually. This process eliminates extra steps in traditional packaging methods, such as wire bonding and separate assembly, reducing labor costs and the chance for defects. This makes CSP an ideal choice for high-volume manufacturing, especially in consumer electronics like smartphones and wearables, where millions of units are produced annually.

Scalability: How CSP Supports Mass Production of Small Devices

Because of its efficient manufacturing process, CSP is highly scalable. This means that companies can produce millions of small, high-performance devices without driving up costs. Whether it’s for a smartphone that requires thousands of camera sensors or a medical device that needs hundreds of tiny chips, CSP enables large-scale production without compromising on quality or increasing prices. The ability to scale up production is one of the reasons CSP is favored in industries that require both cost control and high efficiency.

Key Points:

Wafer-level packaging makes CSP cost-effective by reducing labor and material costs.

CSP’s scalability allows for high-volume production of small devices at low costs.

4. Thin Profile for Ultra-Slim Devices

Small Package Thickness (0.3mm to 1.0mm): Application in Ultra-Thin Devices like Smartwatches and Earbuds

CSP is designed to be incredibly thin, with package thicknesses ranging from 0.3mm to 1.0mm. This thin profile is critical for creating ultra-slim devices like smartwatches and earbuds, where every millimeter of space matters. For example, the thickness of a smartwatch can be just around 2mm, and CSP technology helps pack in high-performance chips without increasing the device's overall thickness. This makes CSP an excellent solution for manufacturers aiming to create sleek, compact products without sacrificing performance.

Key Points:

CSP has a thin profile (0.3mm to 1.0mm), perfect for ultra-slim devices.

Essential for wearables like smartwatches and earbuds that need to remain compact.

Challenges of CSP Packaging

1. Difficult Repair and Rework

Challenges with Manual Repair: Need for Specialized Tools and Difficulty of Rework

One of the main challenges of CSP is the difficulty involved in repairing or reworking damaged chips. Unlike traditional packaging, CSP’s small size and compact design make it very difficult to access individual components once they are assembled. If a chip becomes faulty or needs to be replaced, the repair requires specialized tools like micro-soldering equipment. These tools are precise enough to handle tiny connections, but they are not commonly available for general use, making it difficult for technicians to repair CSP devices without proper training.

For example, in the case of a smartwatch that uses CSP, if the chip is damaged, the tiny connections between the chip and the package can’t be easily fixed by standard tools. This often means that the whole device might need to be replaced, leading to higher repair costs and longer downtime.

Impact on Reusability and Recycling: Limited Reusability Due to Its Small Size

CSP’s small size also limits its reusability and recycling. Because CSP is so tightly packed and the connections are so delicate, it is challenging to extract and reuse the chip or the components once they are mounted. In comparison, traditional packages like BGAs or SOPs are easier to disassemble and reuse. This makes CSP less environmentally friendly, as it increases electronic waste. Additionally, the high precision required for repairs reduces the possibility of reusing parts for other devices.

Key Points:

CSP repairs require specialized tools and are difficult to perform manually.

Reusability is limited due to the small size and complex connections of CSP.

Recycling CSP components is more challenging than traditional packages.

2. Heat Management Limitations

Thermal Challenges: CSP’s Limitation in Dissipating Heat in High-Power Applications

Another significant challenge with CSP is its heat management. In small, compact devices, managing heat is crucial for maintaining performance and preventing damage to the electronics. CSP, due to its compact size, doesn’t have the same ability to dissipate heat as traditional packages. The shorter connections and tightly packed components can trap heat, which might cause overheating in high-power applications.

For example, in 5G devices or gaming consoles, where high processing power is required, the heat generated by the chips can be a problem. If the heat isn’t properly managed, it can affect the device’s performance or even damage internal components. CSP may not be the best solution for these types of high-power devices without additional heat management solutions.

Power Amplifiers and CSP: Why CSP Is Not Suitable for High-Power Applications Over 3W

CSP packaging is typically not suited for applications requiring more than 3 watts of power. Devices like power amplifiers, which are used in telecommunications or high-speed computing, require more advanced heat dissipation techniques due to their high power consumption. CSP’s small size limits the amount of space available for heat sinks or other cooling mechanisms. As a result, CSP is typically avoided in applications that need to handle large amounts of heat, such as in power amplifiers used in high-performance 5G networks.

Key Points:

CSP struggles with heat dissipation, making it unsuitable for high-power devices.

Power amplifiers and devices over 3W are not ideal for CSP packaging.

Thermal management is a key limitation of CSP technology in high-performance applications.

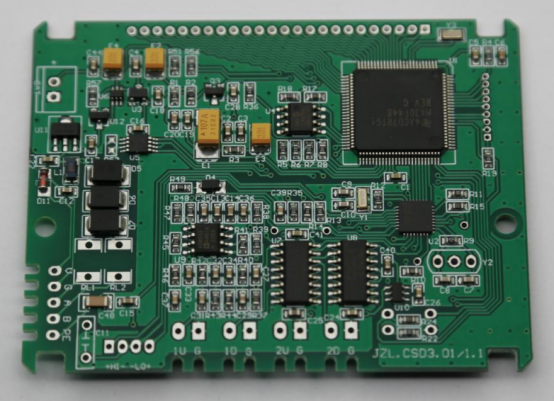

3. Design and Manufacturing Complexity

Need for HDI PCBs: High-Density Interconnect Boards for Trace Routing

CSP requires High-Density Interconnect (HDI) PCBs to accommodate the small size and complex trace routing. HDI PCBs are advanced printed circuit boards that use smaller trace widths and more layers to route signals. The design of these boards is more complex and requires precise manufacturing to ensure that the small traces can handle high-speed signals without interference. HDI PCBs are necessary for CSP to work properly, as traditional PCBs cannot support the tight requirements of CSP's compact design.

The use of HDI PCBs allows for the dense routing needed to connect all the components. However, designing these boards adds complexity to the manufacturing process, making it more expensive and time-consuming.

Challenges in Component Placement: The Complexity of Placing High-Density Components Within a Small Footprint

Another challenge in CSP design is the difficulty of placing high-density components within such a small footprint. In CSP devices, like smartwatches or IoT sensors, every millimeter of space is used for critical components like processors, memory, and sensors. Ensuring that each component is placed in the correct position requires careful planning and advanced techniques. The high density of components also means that there is less room for error during manufacturing, making the production process more complex.

Additionally, component placement must be done with precision to avoid any electrical interference or signal degradation. If the components are not correctly placed or aligned, it can lead to poor device performance or failure.

Key Points:

HDI PCBs are needed for routing in CSP, adding complexity to the design and manufacturing process.

Component placement in CSP is difficult due to the high density of components within a small space.

Designing CSP-based devices requires advanced techniques to ensure proper function and reliability.

Conclusion

CSP is a game-changing technology for creating smaller, more efficient, and high-performance devices. However, its challenges—such as repair difficulties, heat management issues, and design complexity—require careful consideration. Companies like PCBMASTER, with their experience in PCB manufacturing, are well-equipped to support the development of CSP-based devices. With their expertise in HDI PCBs and efficient design solutions, they help ensure the successful implementation of CSP technology, enabling manufacturers to overcome these challenges and bring innovative, reliable devices to market.

FAQs

1. What is the difference between CSP and BGA?

Size, Performance, and Cost Differences

CSP and BGA are both packaging technologies for semiconductor chips, but they differ in size, performance, and cost.

Size: CSP is typically much smaller than BGA. While CSP is designed to be nearly the same size as the chip itself (often no more than 1.2 times the size of the chip), BGA packages are larger and may add extra space around the chip for connections and mounting.

Performance: CSP generally provides better signal integrity and faster data transmission due to its shorter electrical connections, which are key in minimizing signal loss and improving performance in high-speed devices. BGA, on the other hand, can handle more complex connections but is less compact and may have slightly higher inductance and resistance.

Cost: CSP is more cost-effective for high-volume production because of its simple, wafer-level manufacturing process, while BGA packaging is often more expensive due to its larger size and more complex assembly.

2. How does CSP improve device performance?

Technical Explanation of Flip-Chip Bonding and Signal Integrity

CSP improves device performance primarily through flip-chip bonding. In flip-chip bonding, the chip is flipped upside down, and tiny solder bumps connect it directly to the substrate or package. This provides shorter electrical connections between the chip and the package, which reduces signal loss and inductance—two critical factors in high-speed data transmission.

Shorter connections result in faster signal speeds and better signal integrity, which is particularly important in devices requiring high-frequency data transfer, like smartphones, 5G devices, and high-performance processors. The reduction in heat and resistance also contributes to maintaining optimal performance.

3. Can CSP be used for high-power devices?

CSP's Limitations with Heat Dissipation and Power Handling

CSP has limitations when it comes to handling high-power devices. Due to its compact size, CSP struggles with heat dissipation. For devices requiring more than 3 watts of power, like power amplifiers or high-performance processors, CSP may not be the ideal solution. High-power devices generate significant heat, and CSP’s small footprint makes it difficult to include sufficient heat sinks or other cooling mechanisms.

As a result, CSP is typically not used in high-power applications like power amplifiers in telecommunications, where effective heat management is crucial. CSP is better suited for low to medium power applications, such as wearables, smartphones, and IoT devices.

4. Is CSP suitable for small-scale or low-volume production?

Insight on the Manufacturing Cost-Effectiveness of CSP for High-Volume Applications

CSP is best suited for high-volume production rather than small-scale or low-volume manufacturing. The primary reason for this is its cost-efficiency in mass production. The wafer-level packaging process used in CSP allows for packaging multiple chips at once, which reduces per-unit costs when producing large quantities. This makes CSP an ideal choice for products like smartphones and consumer electronics, where millions of units are produced annually.

For small-scale or low-volume production, the specialized equipment and processes involved in CSP manufacturing may not justify the investment, as the cost savings per unit would not be as significant compared to traditional packaging methods.

5. What are the key challenges in designing with CSP?

Overview of the Challenges in Repair, Thermal Management, and PCB Design

Designing with CSP comes with several challenges, including:

Repair and Rework: CSP’s compact size and the use of flip-chip bonding make it difficult to repair or replace individual components. Specialized tools like micro-soldering equipment are needed for repairs, and the tiny connections make it harder to rework or recycle CSP packages compared to traditional packages.

Thermal Management: Due to its small form factor, CSP struggles with heat dissipation, particularly in high-power applications. Devices requiring significant processing power, such as power amplifiers or 5G modules, may experience overheating, which can reduce performance and damage components if not properly managed.

PCB Design: Designing a HDI PCB is essential for CSP because the small size and complex connections require precise trace routing. These boards must be able to accommodate the tiny traces needed to connect the components, which makes the design and manufacturing process more complex. Additionally, the high density of components in CSP devices means there is little room for error, adding complexity to both the design and manufacturing phases.

Author Bio

Hi, I'm Carol, the Overseas Marketing Manager at PCBMASTER, where I focus on expanding international markets and researching PCB and PCBA solutions. Since 2020, I've been deeply involved in helping our company collaborate with global clients, addressing their technical and production needs in the PCB and PCBA sectors. Over these years, I've gained extensive experience and developed a deeper understanding of industry trends, challenges, and technological innovations.

Outside of work, I'm passionate about writing and enjoy sharing industry insights, market developments, and practical tips through my blog. I hope my posts can help you better understand the PCB and PCBA industries and maybe even offer some valuable takeaways. Of course, if you have any thoughts or questions, feel free to leave a comment below—I'd love to hear from you and discuss further!