Mastering PDN Design for High-Speed PCBs: Key Strategies for Signal and Power Integrity

High-speed electronics thrive on a delicate balance of power, precision, and performance. Whether it's the lightning-fast data of 5G networks or the complex systems in autonomous vehicles, one thing is essential: a well-designed Power Distribution Network (PDN). This critical component ensures stable voltage, reduces interference, and maintains signal clarity. A properly engineered PDN doesn’t just improve performance—it’s the foundation that supports the entire system. Getting it right is key to unlocking the full potential of modern technology.

Power Distribution Networks (PDNs) in High-Speed PCBs

What is a PDN in High-Speed PCBs?

A Power Distribution Network (PDN) in high-speed PCBs ensures that all components receive stable, clean power. It consists of power planes, ground planes, vias, and decoupling capacitors, working together to minimize noise and voltage fluctuations. In high-speed devices like 5G routers and data center servers, a well-designed PDN is crucial for reliable performance.

Importance of PDN in High-Performance Devices

The PDN is vital for ensuring efficient power delivery in high-performance devices such as 5G routers, data center servers, and automotive systems. It prevents issues like voltage drops and electromagnetic interference (EMI), which can affect device performance and reliability.

Role in High-Performance Devices

A strong PDN design supports performance, efficiency, and reliability. For example, in data center servers, the PDN delivers stable power to thousands of components. In autonomous vehicles, it ensures safe operation of sensors and control systems by providing consistent power.

Why PDN Design Matters in High-Speed Applications

Impact of Poor PDN Design

Voltage Drops: Voltage drops can cause components to malfunction or fail, especially in data centers where servers need consistent power to function properly.

EMI: A poorly designed PDN can increase EMI, leading to signal degradation and slower data speeds in devices like 5G routers.

Signal Integrity Issues: Problems like ringing and crosstalk occur when the PDN is inadequate, which can corrupt data and disrupt communication, especially in autonomous vehicles.

System Failures: PDN failures can cause critical systems to stop working, leading to device crashes or total system shutdowns.

System Performance and Reliability

A properly designed PDN ensures stable power delivery, minimizes noise, and improves signal integrity. This leads to better performance and long-term reliability of devices like 5G routers, data centers, and automotive systems, ensuring they run efficiently over time.

Core Principles of PDN Design in High-Speed PCBs

Power Integrity (PI) in High-Speed PCBs

Achieving Stable Voltage Delivery

Stable voltage is crucial for the reliable operation of high-speed systems, such as 5G routers, data center servers, and automotive electronics. Ensuring Power Integrity (PI) is key to maintaining this stable voltage. If the voltage supplied to the components fluctuates or drops, it can cause performance issues like system crashes, slowdowns, or even component damage. A stable power supply, supported by good Power Integrity, ensures that all circuits operate correctly and reliably at high frequencies, minimizing the risk of errors or failures in these critical systems.

Key Strategies for Stable Power Delivery:

1. Solid Power Planes

Solid, uninterrupted power planes are essential for maintaining consistent voltage. These planes act as large conductive layers that distribute power evenly across the PCB. Interruptions in the power plane, such as gaps or excessive resistance, can cause voltage drops and lead to system instability. Ensuring the power plane is as continuous and solid as possible helps prevent power delivery issues.

2. Decoupling Capacitors

Decoupling capacitors are small components placed near power supply pins to filter out noise and smooth out any voltage spikes. They provide local energy storage, which helps maintain steady voltage, especially when the system requires sudden bursts of power. By filtering high-frequency noise, decoupling capacitors help ensure the reliability of the circuit, especially in high-speed applications.

3. Low-Impedance Paths

Low-impedance paths are essential for minimizing voltage fluctuations and ensuring the power delivered is as stable as possible. High-impedance paths cause power loss and introduce noise, which can degrade the performance of high-speed systems. Ensuring the PDN has low impedance helps maintain a steady voltage across all components, improving overall system stability.

Impedance Requirements for Stable Power

For a PDN to work efficiently, it must maintain low impedance, ideally under 1 ohm. High impedance leads to voltage drops, especially when current increases, which can result in performance degradation.

The impedance must also be consistent across different frequency ranges, particularly from 1 kHz to 100 MHz, where many high-speed systems operate. Variations in impedance can cause power noise and affect the functioning of sensitive components. By ensuring impedance stability, the PDN minimizes power-related issues and keeps the system running smoothly.

Signal Integrity (SI) and Its Relationship with PDN

Effects of PDN on Signal Integrity

A poorly designed PDN can introduce unwanted noise into the system, leading to signal integrity (SI) issues. Signal integrity refers to the quality of the electrical signals being transmitted through the PCB. If the power delivery is unstable or noisy, it can distort the signals, leading to problems such as ringing, overshoot, and crosstalk.

1. Ringing occurs when the signal bounces back after passing through a component, creating unwanted oscillations that interfere with the correct transmission of data.

2. Overshoot happens when the voltage level of a signal exceeds its intended value, causing inaccuracies and potential errors in high-speed circuits.

3. Crosstalk is interference between nearby signals, where one signal unintentionally affects another, causing noise and data corruption.

The relationship between the PDN and signal integrity is direct. A noisy PDN or one that introduces voltage fluctuations can corrupt the signals, leading to significant performance degradation.

Maintaining Clean Power for Clean Signals

1. Decoupling Capacitors

By placing decoupling capacitors at strategic points in the design, designers can reduce noise and ensure clean power. These capacitors help remove high-frequency noise from the PDN, ensuring that the signals remain clear and distortion-free. This is especially important in high-speed designs, where signal clarity is crucial.

2. Low-Impedance Return Paths

Ensuring low-impedance return paths for signals helps to minimize the risk of signal distortion. A low-impedance return path allows the signals to return to the power supply with minimal interference, keeping the system running at optimal performance. High-impedance return paths can introduce noise and cause signal quality issues.

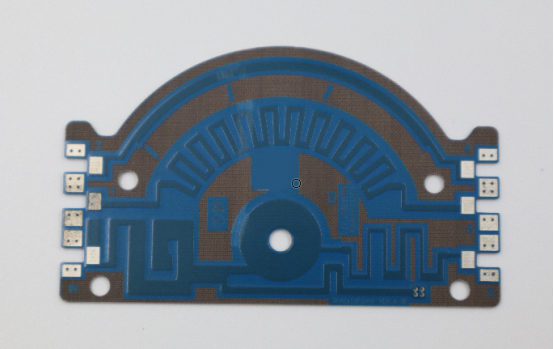

Layer Stack-Up Optimization for Effective PDN

Designing Layer Stack-Ups for Power and Signal Integrity

The layer stack-up refers to how the layers of the PCB are arranged. Proper stack-up design is essential for maintaining both power and signal integrity. A well-designed stack-up can minimize noise, reduce EMI, and ensure a stable PDN.

1. Pairing Power and Ground Planes

Pairing power and ground planes helps provide the necessary capacitance between them, which is essential for effective power delivery and noise reduction. A well-paired power and ground plane improves the PDN’s ability to deliver stable voltage and reduces the likelihood of EMI. The closer the power and ground planes are, the better the capacitance and noise shielding.

2. Shielding High-Speed Signals

Using dedicated layers to shield high-speed signals from noise helps maintain signal integrity. High-speed signals are particularly sensitive to interference, and proper shielding ensures that they remain clean and unaffected by power fluctuations or other signals. Shielding also minimizes crosstalk between nearby traces, further improving signal quality.

3. Ensuring Symmetrical Stack-Ups

Symmetry in the stack-up is important for maintaining a balanced PDN. A symmetrical stack-up helps ensure even distribution of power across the PCB, reduces EMI, and enhances signal integrity. A well-balanced stack-up ensures that power delivery is consistent and that the high-speed signals are routed effectively without interference.

Key Design Considerations for Optimizing PDN in High-Speed PCBs

Decoupling Capacitors

Capacitor Selection

Decoupling capacitors are essential components in a Power Distribution Network (PDN). They help maintain stable power delivery by filtering out unwanted noise, smoothing voltage fluctuations, and providing local energy storage. Choosing the right capacitor depends on the frequency range of the signals the PCB will handle.

Low-frequency capacitors (e.g., electrolytic capacitors) are often used for filtering low-frequency noise, while ceramic capacitors are preferred for high-frequency applications because of their low impedance at higher frequencies.

For high-speed systems like 5G routers or data centers, ceramic capacitors with a low equivalent series resistance (ESR) are ideal for providing quick response times to power fluctuations.

Placement and Density

Proper placement and density of decoupling capacitors are critical to optimizing the PDN. Capacitors should be placed as close as possible to the power pins of the components they are decoupling. This reduces the path resistance and inductance, ensuring that they can effectively smooth out voltage spikes and noise.

Strategic placement: Place capacitors near high-speed components, such as processors or memory modules, where power demand fluctuates rapidly.

Density: Using multiple capacitors in parallel across the board can improve current delivery and noise filtering, as different capacitors filter different frequency ranges.

Capacitor Sizes

The size of the capacitor also plays a crucial role in filtering various frequency ranges. Small capacitors (e.g., 0.1 µF ceramics) are effective at filtering high-frequency noise, while larger capacitors (e.g., 10 µF or higher) handle lower frequencies and provide more bulk energy storage.

Small capacitors: Best for filtering high-frequency noise above 100 MHz.

Larger capacitors: Better suited for lower frequencies, ensuring stable voltage during sudden current draws.

A balanced approach, combining both small and large capacitors, helps optimize the frequency response of the PDN across a wide range of signal frequencies.

Via Design and Optimization

Reducing Via Inductance

Vias are used to connect different layers of a PCB, allowing power to flow across the board. However, vias introduce inductance, which can impact the performance of the PDN, particularly at high frequencies. The inductance of a via creates a high impedance path for the power, which can lead to voltage drops and affect the overall stability of the PDN.

Via size: Larger vias have lower inductance because they can carry more current without creating excessive resistance.

Via plating: Ensuring proper plating inside the via reduces the resistance and minimizes inductance, improving power delivery.

To maintain low impedance, the via design should focus on minimizing resistance and inductance to maintain clean and stable power delivery, especially in high-speed applications.

Multi-Via Solutions

Using multiple vias in parallel is an effective strategy for reducing via inductance and ensuring low impedance across the PDN. This technique distributes current across multiple paths, improving the stability and capacity of the power network.

Benefits: Multi-via solutions reduce the overall resistance and inductance of the power delivery system, ensuring better current handling and faster response times.

Design consideration: Ensure vias are placed in close proximity to each other and the components they power for the most effective power delivery.

By integrating multiple vias into the design, the PDN can handle high current demands without suffering from excessive voltage drops or power loss.

Power and Ground Plane Design

Solid vs. Split Planes

The design of the power and ground planes plays a major role in ensuring efficient power distribution. Two common approaches are solid planes and split planes.

Solid planes: These are continuous layers of power and ground that provide uninterrupted paths for power delivery. They are ideal for low-noise environments and ensure stable voltage across the PCB.

Split planes: In some cases, power and ground are separated into different sections to reduce noise between circuits. This can be useful in specific designs, such as when isolating high-power components from sensitive signal traces. However, split planes can introduce challenges like increased impedance and uneven current distribution.

For most high-speed designs, solid power and ground planes are preferred because they provide better noise filtering and more reliable power delivery across the PCB.

Plane Resonance Issues

Plane resonance occurs when the power or ground planes act like a capacitor, leading to oscillations at certain frequencies. These oscillations can cause power noise and affect the performance of high-speed circuits.

Issue: If the resonant frequency of the plane aligns with the operating frequency of the circuit, it can cause unwanted interference, which degrades signal integrity and system stability.

Mitigation: To reduce plane resonance, designers can use thicker planes, add decoupling capacitors at strategic points, and ensure proper layer stack-up to shift resonant frequencies away from critical operational frequencies.

By carefully managing plane resonance, designers can ensure the PDN remains stable and supports high-speed, high-performance systems without introducing noise or instability.

Advanced Topics in PDN Design

Power Delivery for Multi-Layer PCBs

Challenges in Multi-Layer PDN Design

As PCBs become more complex, especially in high-speed applications, the number of layers in a design often increases. This adds complexity to the PDN because more layers mean more paths for power delivery, which can lead to issues such as power loss, signal interference, and voltage drops.

Multiple layers can result in increased impedance and coupling between layers, leading to unwanted noise or crosstalk.

As more components are packed into a PCB, the power requirements grow, and ensuring each component receives stable power becomes more challenging. Without proper PDN design, this can lead to performance degradation and system instability.

Effective Layer Pairing

To handle the challenges of multi-layer PDN design, proper layer pairing is essential. The power and ground layers should be paired in a way that maximizes capacitance between them while minimizing noise and interference.

Best practices: Power and ground layers should be placed adjacent to each other to create a low-impedance path for power delivery. This configuration reduces noise and helps maintain voltage stability across the PCB.

In multi-layer designs, ensure that power layers are sandwiched between ground layers for optimal signal integrity and power distribution. This helps minimize noise and ensures a stable PDN.

By optimizing the layer stack-up and choosing the right pairing, engineers can improve power delivery, minimize noise, and increase overall system reliability in complex, multi-layer PCBs.

Impact of PDN on EMI and EMC

Reducing EMI

EMI is a major concern in high-speed PCB designs. EMI occurs when electromagnetic waves from high-speed signals interfere with other circuits, causing noise and reducing signal integrity. The PDN design plays a crucial role in reducing EMI by providing stable, clean power to components while minimizing noise propagation.

Proper PDN design can reduce power plane noise and minimize the risk of radiated emissions, which can affect other devices or cause the system to malfunction.

Strategies such as low-impedance power delivery paths, proper decoupling, and strategic placement of power planes can significantly reduce the amount of electromagnetic interference generated by the system.

By designing a well-balanced PDN, the amount of radiated EMI is minimized, making the system more reliable and compatible with regulatory standards for Electromagnetic Compatibility (EMC).

Shielding and Filtering

The PDN plays a key role in improving EMC by incorporating shielding and filtering techniques. These techniques help isolate sensitive circuits from noise sources and reduce the overall electromagnetic footprint of the device.

Shielding: This involves using layers or materials to protect high-speed signals from external interference and to prevent the leakage of noise from the PDN into the surrounding environment.

Filtering: Using decoupling capacitors and other components to filter out high-frequency noise from the power supply helps maintain clean power and stable signals.

By carefully designing the PDN to include proper shielding and filtering, it is possible to improve EMC, reduce interference between components, and ensure that the system operates reliably in various environments.

High-Speed and High-Frequency Considerations

Signal Integrity at High Frequencies

In high-speed designs, especially those operating at GHz frequencies (e.g., 5G systems, high-speed memory, and processors), maintaining signal integrity is critical. The PDN must support clean and stable power delivery while minimizing noise and ensuring that signals are transmitted accurately.

High-frequency signals are particularly sensitive to power supply fluctuations. A poorly designed PDN can introduce noise that causes signal degradation, leading to issues such as ringing, overshoot, and crosstalk.

To support high-speed signals, the PDN should provide low impedance paths and avoid introducing unwanted noise into the system. Proper placement of decoupling capacitors and low-impedance return paths can help maintain signal clarity even at high frequencies.

By focusing on signal integrity and ensuring that the PDN is optimized for high-frequency applications, designers can ensure that the system operates without signal distortion or data errors.

Simulation and Modeling

Before finalizing a PDN design, engineers use simulation tools to model how the PDN will behave in a real-world environment. Simulation allows designers to predict performance, identify potential issues, and optimize the PDN for high-speed circuits.

PI simulations: These tools help visualize voltage drops, current distribution, and impedance changes across the PCB, ensuring that the PDN can handle the power demands of high-speed circuits.

SI simulations: These simulations focus on the behavior of signals as they travel through the PCB, allowing engineers to detect potential issues like crosstalk, reflection, and noise.

Electromagnetic simulations: Tools that predict the amount of EMI generated by the PDN, helping engineers design shielding and filtering techniques to reduce interference.

Using these simulation and modeling tools, engineers can fine-tune the PDN design, ensuring that the system will meet performance and reliability requirements even in complex, high-speed environments.

Practical PDN Design Strategies for High-Speed Applications

Designing for 5G Routers

High-Speed Requirements of 5G

The PDN plays a critical role in the performance and reliability of 5G routers. 5G networks require the transfer of large amounts of data at incredibly high speeds, making the stability and efficiency of the PDN essential for smooth operation. If the PDN does not deliver clean, stable power, the performance of the router could degrade, causing issues like dropped connections, slow speeds, or signal interference.

At the heart of 5G routers are components that operate at high frequencies, which means that the PDN must ensure consistent voltage and low-noise power delivery. Any disruption in power delivery can lead to signal distortion, data errors, or even system crashes.

Power Requirements for 5G

5G applications demand high power to handle massive data transmission while ensuring signal integrity. The PDN must supply enough power to support these high-performance components, like the baseband processors and radio-frequency (RF) circuits, while maintaining signal quality.

Decoupling capacitors play a critical role in filtering out noise from the power supply, ensuring clean power to sensitive components.

Low-impedance paths are necessary to prevent voltage fluctuations and power loss, which could affect the efficiency and reliability of 5G routers.

High-speed components like RF amplifiers require precise power delivery to avoid performance issues such as signal degradation or interference.

Designing the PDN for 5G routers involves balancing the need for high power with the need for signal purity. Effective PDN design in this context ensures that the router can handle heavy data loads while maintaining strong, uninterrupted signals.

PDN in Data Center Servers

High-Density Circuits

In data center servers, the PDN design faces unique challenges due to the high density of components packed into the motherboard. These servers contain multiple high-performance processors, memory modules, and storage devices that demand significant power.

As components are packed more densely on the PCB, the available space for routing power and ground planes becomes limited.

The increased current draw and complexity of the circuits lead to greater challenges in managing power distribution while maintaining low-impedance paths.

The design must focus on optimizing power plane pairing, ensuring uniform power distribution, and minimizing voltage drops across the board. The PDN must also ensure that noise from high-speed components like processors does not interfere with the power supply.

Efficient Power Distribution

Efficient power distribution in data center servers is essential for stable performance, especially when dealing with high-performance processors, such as multi-core CPUs and GPUs, and large memory banks. These components require consistent voltage and current to operate efficiently.

Decoupling capacitors are crucial for reducing noise and stabilizing power supply voltage. By placing capacitors close to high-speed components, such as CPUs and memory, the PDN ensures smooth, uninterrupted power delivery.

Multiple vias should be used to reduce via inductance and ensure that power can flow efficiently through the PCB. This reduces voltage fluctuations and ensures that all components receive the power they need.

Power planes should be designed with low impedance to prevent power loss and maintain a stable environment for all components. This helps in avoiding system failures and slowdowns due to insufficient power.

For data centers, optimizing the PDN ensures that the servers can handle large data loads, high processing speeds, and 24/7 operations without performance degradation or failure.

Automotive Systems and PDN

Power Delivery in Automotive Electronics

Automotive systems, such as autonomous vehicles and advanced driver-assistance systems (ADAS), have unique power delivery requirements. The harsh environments that automotive systems operate in—extreme temperatures, vibrations, and EMI—make designing a reliable PDN crucial.

The PDN must ensure that critical systems, such as safety sensors, braking systems, and navigation, receive stable power at all times, even under extreme conditions.

PI is crucial in automotive systems. If the PDN fails to supply stable voltage, it can result in sensor malfunctions, navigation errors, or failures in safety-critical systems.

The PDN design should focus on delivering clean, stable power while minimizing noise interference and providing redundancy in case of component failure.

Safety and Redundancy

Safety is a top priority in automotive systems, and the PDN plays a significant role in ensuring the reliability and redundancy of these systems. Automotive systems often require dual-redundant power supplies, ensuring that if one power path fails, another can immediately take over, preventing system failure.

Redundant power paths: The PDN should include multiple power sources and paths to ensure that power is always available to critical components.

Temperature resilience: Automotive systems must be designed to withstand extreme temperature fluctuations. The PDN should include components, like temperature-compensating capacitors, that can handle these challenges.

EMC: Automotive systems are subject to significant EMI from engines, motors, and external sources. The PDN must include shielding and filtering to prevent noise from affecting sensitive electronics.

The PDN design for automotive systems focuses not only on power reliability but also on safety and redundancy, ensuring that the system can continue to function reliably, even in the event of a failure.

Conclusion

The design of the PDN is critical for the performance and reliability of high-speed PCBs used in 5G, data centers, and automotive systems. Ensuring power integrity, signal integrity, and optimizing the layer stack-up are essential for stable power delivery and preventing issues like voltage drops and signal interference.

Looking forward, PDN design will continue to evolve with higher-frequency applications and a growing focus on energy-efficient solutions, supported by advanced simulation tools.

In high-speed electronics, a well-designed PDN is key to reliable performance. PCBMASTER offers quality PCB solutions that help address these challenges, ensuring stable power and optimal signal integrity in complex designs.

FAQs

What are the key challenges in designing a PDN for high-speed PCBs?

Designing a PDN for high-speed PCBs presents several challenges, including managing voltage fluctuations, EMI, and ensuring signal integrity at high frequencies. As high-speed systems demand more power, balancing power delivery with noise reduction becomes more complex. Additionally, the increasing density of components and layers in advanced PCB designs requires careful optimization of layer stack-ups and decoupling strategies.

How does PDN design impact the performance of 5G routers specifically?

In 5G routers, the PDN is crucial for ensuring stable power to high-frequency components like RF amplifiers and baseband processors. If the PDN fails to deliver clean power, it can lead to signal degradation, data errors, and even connection drops. Effective PDN design involves managing voltage stability, minimizing noise, and ensuring low-impedance power delivery to meet the high-speed data demands of 5G applications.

What role does PDN design play in automotive systems?

In automotive electronics, the PDN ensures that safety-critical systems such as ADAS and sensors receive stable, reliable power under harsh conditions like extreme temperatures and vibrations. The PDN must also include redundancy to ensure safety, so if one power path fails, another can take over, preventing system malfunctions. Additionally, the PDN must handle EMI and minimize noise to maintain system integrity in noisy automotive environments.

Author Bio

Hi, I'm Carol, the Overseas Marketing Manager at PCBMASTER, where I focus on expanding international markets and researching PCB and PCBA solutions. Since 2020, I've been deeply involved in helping our company collaborate with global clients, addressing their technical and production needs in the PCB and PCBA sectors. Over these years, I've gained extensive experience and developed a deeper understanding of industry trends, challenges, and technological innovations.

Outside of work, I'm passionate about writing and enjoy sharing industry insights, market developments, and practical tips through my blog. I hope my posts can help you better understand the PCB and PCBA industries and maybe even offer some valuable takeaways. Of course, if you have any thoughts or questions, feel free to leave a comment below—I'd love to hear from you and discuss further!