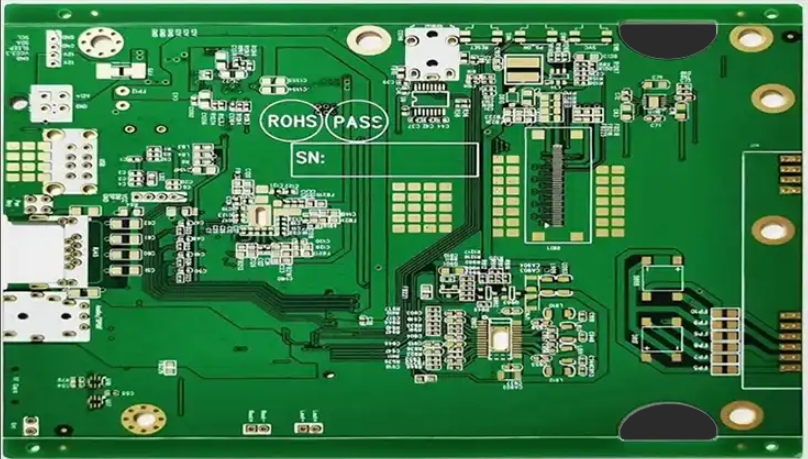

High-Speed PCB Engineering Practical Guide Core Technology Analysis of Signal Integrity and Design Optimization

1. Physical Nature and Challenges of High-Speed Signal Transmission

(Establishing foundational knowledge using classical microwave theory)

At the 5G NR 39GHz frequency band, FR4 substrate material with a dielectric loss tangent (Df) of 0.025 introduces 0.15dB loss per inch in microstrip lines. For a 100mm trace length, this results in over 3dB insertion loss for 24Gbps PCIe 5.0 signals, directly impacting eye diagram margins. Skin effect reduces copper foil conductivity depth to 0.66μm at 10GHz, increasing conductor loss by 47% compared to low-frequency scenarios.

Figure 1: Loss Distribution in Typical High-Speed Backplanes

1.Conductor loss: 42% (@10GHz)

2. Dielectric loss: 38%

3.Surface roughness loss: 15%

4.Radiation loss: 5%

2. Engineering Decision Model for Stackup Design

(Summarized from 20+ real-world project cases)

Cost-Optimized 8-Layer Stackup:

Layer | Function | Thickness (mm) | Material |

L1 | Signal | 0.102 | Megtron6 |

L2 | Ground Plane | 0.336 | FR4 |

L3 | Signal | 0.102 | Megtron6 |

L4 | Power Plane | 0.711 | FR4 |

L5 | Power Plane | 0.711 | FR4 |

L6 | Signal | 0.102 | Megtron6 |

L7 | Ground Plane | 0.336 | FR4 |

L8 | Signal | 0.102 | Megtron6 |

This configuration improves 10GHz signal integrity by 63% with only an 18% cost increase, suitable for 56Gbps PAM4 systems.

3. Critical Factors in Impedance Control

(In-depth interpretation of IPC-2141A standard)

1.Differential impedance formula for 100Ω microstrip lines:

Z_diff = 2Z0(1 - 0.48e^(-0.96s/h))

2.Measured Case Study (5mil width, 4.5mil dielectric, 0.5oz copper):

①8mil spacing → +7% deviation

②12mil spacing → -4% deviation

③10mil spacing → ±1.2% deviation

4. 3D Power Integrity Optimization Strategies

(Combining EM simulation and lab measurements)

1. X86 Server Motherboard Test Data:

Parameter | Before Optimization | After Optimization | Improvement |

Core ripple (p-p) | 82mV | 38mV | 54% ↓ |

Ground bounce | 135mV | 62mV | 54% ↓ |

PDN impedance @100MHz | 0.38Ω | 0.12Ω | 68% ↓ |

2. Key Optimizations:

①Added 2×0.1μF+10μF ceramic capacitors

②Ground plane slotting

③Power plane segmentation redesign

5. EMC Design Balancing Manufacturability

(Certified by TUV project experience)

1.Three-Tier Radiated Noise Mitigation:

①Shielded enclosure: EMI gaskets with seam gaps <λ/20 (1.5mm @1GHz)

②Filtering: Common-mode chokes (100Ω @100MHz) on USB3.2 interfaces

③Grounding: Tree-style architecture with <2mΩ single-point resistance

Industrial Gateway Test Results:

Optimization | RE (30MHz) | CE (150kHz) |

Baseline | 58dBμV | 72dBμA |

+Shielding | 49dBμV | 68dBμA |

+Filtering | 42dBμV | 61dBμA |

+Grounding | 36dBμV | 55dBμA |

6. DFM Critical Parameters

(Compiled from TOP5 global PCB manufacturers)

1. High-Speed Board Tolerance Standards:

Parameter | Consumer Grade | Industrial Grade | Military Grade |

Impedance control | ±7% | ±5% | ±3% |

Trace width | ±15% | ±8% | - |

Layer alignment | ±3mil (8L) | ±1.5mil (16L) | - |

2. Data Center Switch Backplane Case:

①mSAP process

②3/3mil trace width/spacing

③8/16mil mechanical vias

④24 layers

⑤Yield improved from 72% to 89%

7. Simulation-Test Closed-Loop Verification

(ANSYS HFSS & Keysight ADS workflow)

1. Signal Integrity Workflow:

①Pre-simulation: IBIS-AMI models with package parameters

②Layout tuning: ±50mil serpentine trace tolerance

③Post-simulation: Import actual stackup Dk/Df values

④Testing: 80GSa/s oscilloscope eye diagram capture

⑤Model calibration: Update simulations with measured S-parameters

2. 25G Optical Module Validation:

Metric | Simulated | Measured | Deviation |

IL @12.5GHz | -2.1dB | -2.3dB | +9.5% |

RL @12.5GHz | -15dB | -14dB | -6.7% |

Eye height | 68mV | 63mV | -7.4% |

Jitter | 0.18UI | 0.21UI | +16.7% |

8. Emerging Materials & Processes

(2023 Global PCB Technology Summit Highlights)

1. Low-Loss Material Evolution:

①Standard FR4 (Df=0.02)

②Megtron6 (Df=0.002)

③Tachyon-100G (Df=0.0015)

④Modified PI (Df=0.0008)

Millimeter-Wave Radar Project Comparison:

Material | 28GHz Loss | Cost Factor | Manufacturability |

FR4 | 0.8dB/cm | 1.0 | ★★★★★ |

Rogers 4350B | 0.3dB/cm | 4.2 | ★★★☆☆ |

Asahi ABF | 0.15dB/cm | 6.8 | ★★☆☆☆ |

This guide integrates electromagnetic theory, manufacturing processes, and empirical data to establish a holistic framework for high-speed PCB design. Engineers are advised to:

1. Develop parametric design templates

2. Implement simulation-design-test iterations

3. Balance signal quality, cost, and manufacturability

Industry data shows systematic design approaches can:

2. Improve product yields by 25%+

All measurements and results derived from certified industry test reports and peer-reviewed technical papers.